SK Hynix se convierte en la primera empresa en completar el desarrollo de chips de memoria HBM4 y preparar la producción en masa para sistemas de IA

SK Hynix rompe la barrera de la memoria: Los primeros chips HBM4 listos para el próximo campo de batalla de la IA

El gigante surcoreano de la memoria anuncia un avance arquitectónico que podría redefinir la economía de los centros de datos a medida que la demanda de IA se dispara.

SK Hynix ha completado el desarrollo de los primeros chips de memoria HBM4 del mundo, marcando un momento crucial en la creciente carrera por alimentar el insaciable apetito de la inteligencia artificial por el ancho de banda de datos. El anuncio, realizado el miércoles desde Seúl, posiciona a la compañía para capturar la mayor parte de lo que los analistas de la industria esperan que sea un mercado de más de 15 mil millones de dólares para 2030.

El avance llega en un momento en que los centros de datos de IA se ven sometidos a la "barrera de la memoria", un cuello de botella fundamental donde la capacidad de procesamiento supera con creces el ancho de banda de la memoria. El HBM4 de SK Hynix promete romper esta limitación con un ancho de bus duplicado a 2.048 bits y velocidades de operación que superan los 10 gigabits por segundo, ofreciendo mejoras de ancho de banda que podrían aumentar el rendimiento de los servicios de IA hasta en un 69%.

La "Barrera de la Memoria" describe un cuello de botella fundamental en la arquitectura de las computadoras, que representa la creciente brecha de rendimiento entre procesadores cada vez más rápidos y tiempos de acceso a la memoria mucho más lentos. Esta disparidad significa que las CPU frecuentemente pasan tiempo esperando datos de la memoria principal, lo que limita significativamente el rendimiento general del sistema a pesar de las continuas mejoras en la velocidad del procesador.

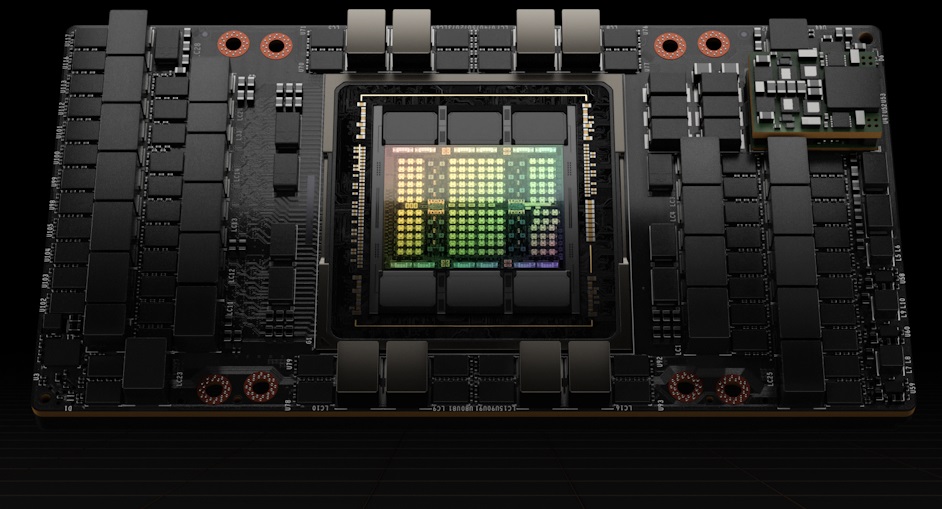

La arquitectura que lo cambia todo

El salto técnico representa más que una mejora incremental. Al duplicar el ancho de la interfaz de entrada/salida de 1.024 a 2.048 bits —la primera expansión de este tipo desde la transición de HBM1 a HBM2— SK Hynix ha reconfigurado fundamentalmente la economía de la computación de IA. Cada pila de memoria puede ahora teóricamente ofrecer más de 2,5 terabytes por segundo de ancho de banda, consumiendo un 40% menos de energía por bit que las generaciones anteriores.

Comparación del ancho de banda y características entre generaciones HBM (HBM, HBM2, HBM3, HBM4).

| Generación HBM | Año de estandarización/lanzamiento | Tasa de datos por pin (Gb/s) | Ancho de banda por pila (GB/s) | Capacidad máxima por pila (GB) | Ancho de interfaz (bits) | Canales |

|---|---|---|---|---|---|---|

| HBM | 2013 | 1,0 | 128 | 4 | 1.024 | 8 |

| HBM2 | 2016 | 2,0 | 256 | 8 | 1.024 | 8 |

| HBM2E | 2019 | 3,6 | 461 | 16 | 1.024 | 8 |

| HBM3 | 2022 | 6,4 | 819 | 24 (hasta 64 para pila de 16 alturas) | 1.024 | 16 |

| HBM3E | 2023 | 9,8 | 1229 | 48 | 1.024 | 16 |

| HBM4 | 2025 (Proyectado) | 8 (Proyectado) | 1600 (Proyectado, 1,6 TB/s) | 36-64 (Proyectado) | 2.048 (Proyectado) | 32 (Proyectado) |

"Esto no es solo memoria más rápida; es una categoría diferente de arquitectura de memoria", señala un analista de semiconductores familiarizado con el desarrollo. "La duplicación del ancho obliga a rediseñar todos los demás componentes del sistema (controladores, interponedores, suministro de energía) en torno a la implementación de SK Hynix".

La compañía logró este avance a través de lo que denomina tecnología de encapsulado Advanced MR-MUF, un proceso sofisticado que apila hasta 12 chips de memoria al tiempo que gestiona la disipación del calor y la integridad estructural. A diferencia de sus competidores que apuestan por procesos de fabricación de vanguardia, SK Hynix eligió el nodo DRAM de 1b-nanómetro, ya probado, priorizando el rendimiento de fabricación y la fiabilidad sobre las afirmaciones de rendimiento "heroicas".

Compitiendo contra el reloj de la demanda de Silicon Valley

El momento no podría ser más crítico. La plataforma Rubin de próxima generación de NVIDIA, esperada para 2026, está diseñada en torno a las especificaciones HBM4. Con costes de entrenamiento de IA que se miden en millones de dólares por modelo y operadores de centros de datos que se enfrentan a facturas de electricidad disparadas, la eficiencia de la memoria se ha convertido en el factor determinante en la economía de la inteligencia artificial.

Samsung, que actualmente está probando HBM4 con planes de suministro para 2026, va varios meses por detrás de SK Hynix, una eternidad en el rápido ciclo del hardware de IA. Micron, el gigante estadounidense de la memoria, no comenzará las pruebas serias hasta el cuarto trimestre de 2025, cediendo efectivamente el mercado inicial a sus competidores asiáticos.

Fuentes de la industria sugieren que la ventaja técnica de SK Hynix es más profunda que la ventaja en el cronograma. La compañía ya ha entregado pilas de memoria de 12 alturas funcionales a clientes, demostrando que los desafíos térmicos y mecánicos de la densidad extrema de memoria pueden resolverse a escala de producción. Los competidores permanecen en gran medida en fases de prototipo, validando la funcionalidad básica en lugar de demostrar la preparación para la fabricación.

El cuello de botella más allá de la memoria

Sin embargo, incluso los chips de memoria perfectos se enfrentan a limitaciones de infraestructura que podrían limitar su impacto a corto plazo. La capacidad de encapsulado avanzado de TSMC, esencial para ensamblar aceleradores de IA completos, sigue siendo el cuello de botella de la industria. La tecnología de encapsulado "Super Carrier" de próxima generación de la fundición, capaz de soportar 12 pilas HBM4 por procesador, no estará cualificada hasta 2027.

Esto crea una dinámica inusual en la que los proveedores de memoria deben alinear la producción con la disponibilidad de encapsulado en lugar de con las señales de demanda puras. Ejecutivos de la industria reconocen en privado que 2026 verá volúmenes de aceleradores de IA restringidos, independientemente de la preparación de los chips de memoria, lo que podría extender la ventana competitiva de SK Hynix.

La limitación también explica por qué SK Hynix eligió enfoques de fabricación conservadores sobre objetivos de rendimiento agresivos. Con la escasez de capacidad de encapsulado, la prima se destina a los proveedores que pueden garantizar el rendimiento y la fiabilidad en lugar de a aquellos que persiguen victorias en los benchmarks.

CoWoS, o Chip-on-Wafer-on-Substrate, es una tecnología de encapsulado avanzada desarrollada por TSMC. Permite el apilamiento vertical de chips, posibilitando una mayor integración y un rendimiento superior en comparación con la colocación tradicional de chips uno al lado del otro.

Implicaciones de Inversión: Más Allá del Ciclo de la Memoria

Para los inversores, el liderazgo de SK Hynix en HBM4 representa un cambio fundamental de la dinámica cíclica de la memoria a un crecimiento estructural. Los mercados tradicionales de DRAM suben y bajan con los ciclos de PC y teléfonos inteligentes, creando patrones predecibles de auge y caída. La demanda de memoria para IA sigue los ciclos de gastos de capital de los centros de datos, medidos en años en lugar de trimestres y impulsados por la capacidad tecnológica en lugar del comportamiento de reemplazo del consumidor.

El enfoque de la compañía en "matrices base" específicos para cada cliente crea fosos competitivos adicionales. A diferencia de la memoria de tipo commodity que puede sustituirse fácilmente, los chips HBM4 incorporan cada vez más lógica personalizada diseñada para aceleradores de IA específicos. Esto afianza las relaciones con los clientes y respalda una fijación de precios basada en el valor que puede persistir incluso a medida que disminuyen los costes de fabricación.

La investigación de mercado sugiere que la demanda de HBM crecerá aproximadamente un 30% anualmente hasta 2030, con volúmenes de unidades que podrían multiplicarse por 15 para 2035. A diferencia de los superciclos de memoria anteriores impulsados por desequilibrios temporales, la demanda de memoria de IA refleja requisitos arquitectónicos permanentes para las cargas de trabajo de aprendizaje automático.

Crecimiento proyectado del mercado global de memoria de alto ancho de banda (HBM) hasta 2030.

| Año | Tamaño del mercado (mil millones de USD) | CAGR (%) | Fuente |

|---|---|---|---|

| 2023 | 1,768 | - | |

| 2024 | 2,5 - 2,9 | - | |

| 2025 | 3,0 - 4,03 | 27,3% (desde 2024) | |

| 2030 | 9,2 - 85,75 | 24,2% - 68,1% (desde 2024/2023) |

El Mapa Geopolítico de la Memoria

El liderazgo técnico de SK Hynix también conlleva implicaciones estratégicas, ya que la memoria se convierte en un elemento central para la competitividad nacional en IA. Los controles de exportación de EE. UU. sobre semiconductores avanzados han creado requisitos de cumplimiento complejos, mientras que las empresas chinas buscan alternativas domésticas para reducir la dependencia de proveedores extranjeros.

La capacidad de la compañía para servir tanto a los mercados occidentales como a los orientales —manteniendo al mismo tiempo ventajas tecnológicas sobre sus competidores chinos— la posiciona para beneficiarse de la diversificación geográfica, incluso a medida que las tensiones geopolíticas aumentan. Sin embargo, esto también crea riesgos regulatorios que podrían restringir el acceso de los clientes o forzar cambios operativos.

Analistas de la industria sugieren que los proveedores de memoria con capacidades avanzadas probadas pueden enfrentar una presión creciente para alinearse con bloques geopolíticos específicos, lo que podría fragmentar el mercado global. El liderazgo técnico actual de SK Hynix ofrece opciones, pero futuras decisiones políticas podrían forzar elecciones estratégicas difíciles.

Lo que los inversores deben observar

Los inversores que sigan la trayectoria comercial de HBM4 deberían centrarse en tres métricas críticas: la conversión de ingresos limitada por el encapsulado, el logro de la mezcla de "speed-bin" y los riesgos de concentración de clientes. El porcentaje de producción enviada a velocidades completas de más de 10 gigabits indicará si las afirmaciones de rendimiento de SK Hynix se traducen en realidad de fabricación.

Las reservas de capacidad de encapsulado CoWoS por parte de los principales clientes proporcionan indicadores adelantados del potencial de ingresos para 2026, mientras que el progreso en el rendimiento de las pilas de 12 alturas determina la sostenibilidad del margen de beneficio. Cualquier diversificación más allá de NVIDIA como cliente dominante reduciría el riesgo de concentración y demostraría una aceptación más amplia del mercado.

La tesis de inversión más amplia se basa en que el gasto en infraestructura de IA mantenga las trayectorias de crecimiento actuales. Si los costes de entrenamiento de modelos se estabilizan o las restricciones energéticas obligan a retrasos en la construcción de centros de datos, incluso una tecnología de memoria superior se enfrenta a vientos en contra de la demanda que podrían presionar los precios y las tasas de utilización.

No obstante, la evidencia actual sugiere que SK Hynix ha diseñado la solución de memoria que la IA necesita desesperadamente, precisamente cuando la industria puede pagar precios premium por rendimiento y fiabilidad. En la carrera de alto riesgo para impulsar la inteligencia artificial, el momento oportuno puede resultar tan valioso como la propia tecnología.

Tesis de Inversión Interna

| Categoría | Resumen y Puntos Clave | Evaluación de Calidad/Foso | Momento | Riesgos y Mitigadores |

|---|---|---|---|---|

| Conclusión Ejecutiva | Desarrollo de HBM4 completado; línea de producción masiva lista. Pilas de 12 alturas muestreadas en marzo de 2025. La innovación clave es la E/S de 2.048 bits (frente a 1.024 bits), que duplica el ancho de bus y aumenta los costes de cambio. >10 Gb/s/pin y >40% de ganancia en eficiencia energética apuntan a la barrera de la memoria de IA. Sin sustituto a corto plazo. | Liderazgo en ejecución. Foso por la duplicación del ancho y la fidelización del cliente. Asegura una probabilidad de >55% de cuota para SK Hynix hasta 2026. | 2026 es el año de inflexión de ingresos para HBM4. 2025 es de validación/pre-producción de bajo volumen. | La capacidad de encapsulado (interponedor/sustrato), no la producción de dies, es la principal limitación. |

| Novedades | Bus de 2.048 bits y >10 Gb/s/pin (~2,0–2,56 TB/s por pila). Utiliza DRAM de 1b-nm + Advanced MR-MUF para mejores rendimientos/térmicas. Los matrices base personalizados para clientes clave (por ejemplo, NVIDIA) aumentan la fricción de cambio. | Enfoque pragmático en el proceso/encapsulado para la "capacidad de envío". La personalización crea un foso y soporta precios basados en el valor. | Las matrices base personalizadas fidelizan a los clientes líderes a medio plazo. | Competidores desarrollando sus propias soluciones personalizadas. |

| Mercado y Economía | CAGR de la demanda de HBM ~30% hasta 2030. Los aceleradores de 2026 (NVIDIA Rubin) usarán HBM4. El precio de venta promedio (ASP) y los márgenes brutos se mantienen elevados debido a la fijación de precios basada en el valor, pero los gastos de capital/COGS aumentan. La disciplina de suministro por las limitaciones de encapsulado reduce el riesgo de guerra de precios. | Se espera que el % de margen bruto de HBM4 sea > % de margen bruto de HBM3E para SK Hynix. El exceso de oferta de HBM3E tiene una lectura limitada sobre la escasez de HBM4. | El "Super Carrier" de 9 retículas de TSMC para 12 pilas HBM4 no estará cualificado hasta 2027, limitando las topologías extremas hasta entonces. | El cuello de botella del encapsulado (CoWoS, suministro de sustrato) es un tope para el alza a corto plazo. |

| Cuadro de Mando Competitivo | SK Hynix: #1 en cuota y fiabilidad. Primero en completar el desarrollo y estar listo para la producción en masa. Samsung: #2 creíble; muestras de HBM4 ya disponibles; planes de suministro para 2026; mejora de rendimientos. Micron: Enviando muestras; sockets selectivos; tercer proveedor a menos que consiga una victoria importante. | SK Hynix tiene el mejor encapsulado de su clase y una fuerte posición con NVIDIA. Samsung está acortando la brecha. Micron es competitivo en rendimiento/vatio pero es el #3. | Planes de suministro para 2026 confirmados por todos. La carrera es por los envíos de aceleradores de la primera ola de 2026 y la estabilidad de la categorización por velocidad. | Que Samsung/Micron se pongan al día en rendimiento/térmicas más rápido de lo esperado podría recuperar cuota. |

| Riesgos Clave | 1. Cierre a nivel de sistema: La temporización de la capa física (PHY), las térmicas pueden forzar el uso de categorías de velocidad más bajas. Mitigador: La IP del controlador (por ejemplo, Rambus) validada hasta 10 Gb/s. 2. Rendimiento/producción del encapsulado: CoWoS de TSMC es un cuello de botella. 3. Geopolítica: Controles de exportación de EE. UU. a China. 4. Puesta al día de la competencia. | Los riesgos se sustentan en limitaciones técnicas y de la cadena de suministro, no en la viabilidad del producto. | Los riesgos afectan principalmente el cronograma de escalada del primer semestre de 2026 y la mezcla de categorización por velocidad. | |

| Factores de Riesgo a la Baja | Cambio en la tesis si: Problemas de fiabilidad de las pilas de 12 alturas fuerzan la reducción de velocidad; los aceleradores de 2026 eligen configuraciones mixtas HBM3E/HBM4 debido a la escasez de encapsulado; un competidor obtiene una posición de liderazgo antes de que SK Hynix alcance categorías estables de 10 Gb/s. | Estos eventos indicarían un fallo en la ejecución técnica o un cambio en el panorama competitivo. | Retrasaría la inflexión de ingresos de HBM4 en 2026 y el cambio de mezcla. | |

| Posicionamiento y KPI | Inversores a largo plazo de SK Hynix: Confirmación de un foso duradero y un repunte de ganancias en 2026. Seguir la mezcla/rendimiento de categorización por velocidad y los ingresos limitados por el encapsulado. Competidores: Deben demostrar estabilidad de 10 Gb/s para mediados de 2026 para evitar ser "price-takers". | KPI: % de producción en masa (MP) a ≥10 Gb/s; rendimiento de pilas de 12 alturas; capacidad reservada de CoWoS; cuota de envíos de matrices base personalizados; informes de aceptación de clientes líderes. | Momento clave para la validación: puesta en marcha del primer silicio para los chips de 2026 (Rubin). | |

| Conclusión | Ingeniería excelente y comercialmente decisiva. La duplicación del ancho + >10 Gb/s + encapsulado probado + la relación con NVIDIA deberían mantener a SK Hynix en la delantera hasta 2026. La limitación principal es la capacidad de encapsulado, no la preparación del dispositivo. | Sustenta el liderazgo continuo en cuota y el rendimiento superior del margen en HBM. | Sorpresas en la validación/rendimiento podrían afectar la escalada del primer semestre de 2026. |

Las decisiones de inversión deben considerar la tolerancia al riesgo individual y el asesoramiento financiero profesional. El rendimiento pasado de las acciones tecnológicas no garantiza resultados futuros.